這是關于如何實現PCIe Gen3/Gen4接收端鏈路均衡測試的系列介紹,小泰將分別從理論篇到實踐篇,為您講述PCIe 3.0/4.0的鏈路均衡的工作原理及對鏈路均衡的測試和調試。

本期為理論篇,主要介紹PCIe 3.0&4.0的鏈路均衡,包括:

1)發送端的均衡: FFE

2)接收端的均衡: CTLE和DFE

3)鏈路均衡過程

PCIe接口自從被推出以來,已經成為了PC和Server上重要的接口。為了更高了數據吞吐率,PCI-SIG組織于2010年推出了PCIe 3.0,數據速率達到了8GT/s;于2017年推出了PCIe 4.0,數據速率達到了16GT/s。PCIe 3.0已經是PC上的標配接口;而PCIe 4.0目前仍處于Server上,在PC上也在開始普及。

*,PCIe 1.0和2.0使用的是普通的FR4板材和廉價的接插件。為了實現在這樣的物理介質上進行有效的信號傳輸,PCI-SIG組織使用了8b/10b編碼和發送端的去加重技術,來保證信號質量:

在PCIe 1.0中,去加重值為固定值3.5dB;

在PCI 2.0中,去加重值為3.5dB或6.0dB中的任何一個,也是為固定值,無法動態調整。

但是隨著速率的翻倍,為了在PCIe 3.0和4.0中仍然使用普通的FR4板材以及廉價的接插件。

PCI-SIG組織對規范做了兩方面的改進:

通過這兩方面的改進,PCI-SIG組織實現了在速率翻倍的同時,仍能保持使用普通的FR4板材和廉價接插件。本應用筆記就聚焦于PCIe 3.0和4.0中的動態均衡技術,介紹其原理、實現及其相關的一致性測試。這樣一種動態均衡技術,在spec中被稱作“Link Equalization”(鏈路均衡,簡稱為LEQ)。

▼ ▼ ▼

本系列包含理論篇和實踐篇兩個部分

理論篇主要介紹PCIe 3.0/4.0的鏈路均衡的工作原理。實踐篇則側重于對鏈路均衡的測試和調試。

PCIe 3.0&4.0的鏈路均衡

在PCIe 3.0和4.0中的鏈路均衡技術相較于先前代要復雜得多,這樣一種動態均衡技術可以分為兩個方面進行討論:

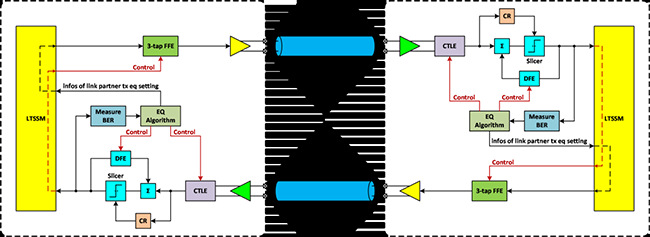

我們先來從均衡特性的角度來看看PCIe 3.0和4.0的均衡,如下圖1展示了在PCIe 3.0/4.0中所使用的全部均衡技術,在Tx端有FFE(Feed Forward Equalizer,前饋均衡器);在Rx端有:CTLE(Continuous Time Linear Equalizer,連續時間線性均衡器)和DFE(Decision Feedback Equalizer,判決反饋均衡器)。

圖1. LEQ硬件實現的模塊框圖

通過FFE和CTLE,可以去除大部分由ISI所引入的抖動;通過DFE可以進一步去除ISI,它還能去除部分的阻抗失配所造成的反射。通過這些均衡處理,就能夠保證在接收端判決輸入處將眼圖打開。

除了上述這些均衡特性上的支持外,在協議層(LTSSM)中還規定需要通過協議的方式來動態調整鏈路上的均衡設定值,這整個過程稱作鏈路均衡(Link Equalization,LEQ)。

在鏈路均衡過程中:

本地端按照某個初始Tx EQ的設定來發送數據;

對端在接收到數據時,會根據誤碼率或信號質量來判斷該Tx EQ是否合適;

若不合適,對端會通過協議向本地端請求一個新的Tx EQ值;

本地端在接收到這個請求值之后,會改變Tx EQ的值。

通過這一動態過程,就能夠保證鏈路上的Tx EQ為優值。與此同時,本地端和對端也會同時調整Rx EQ。通過動態地調整Tx EQ和Rx EQ,就能夠靈活地適應不同的信道情況。